-

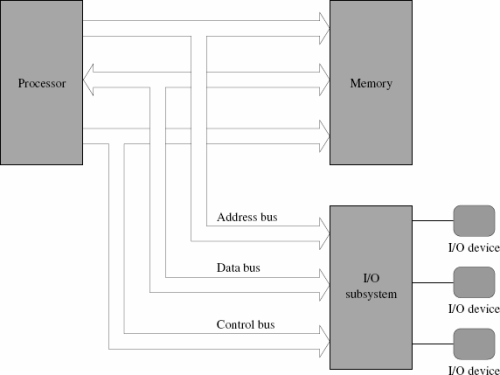

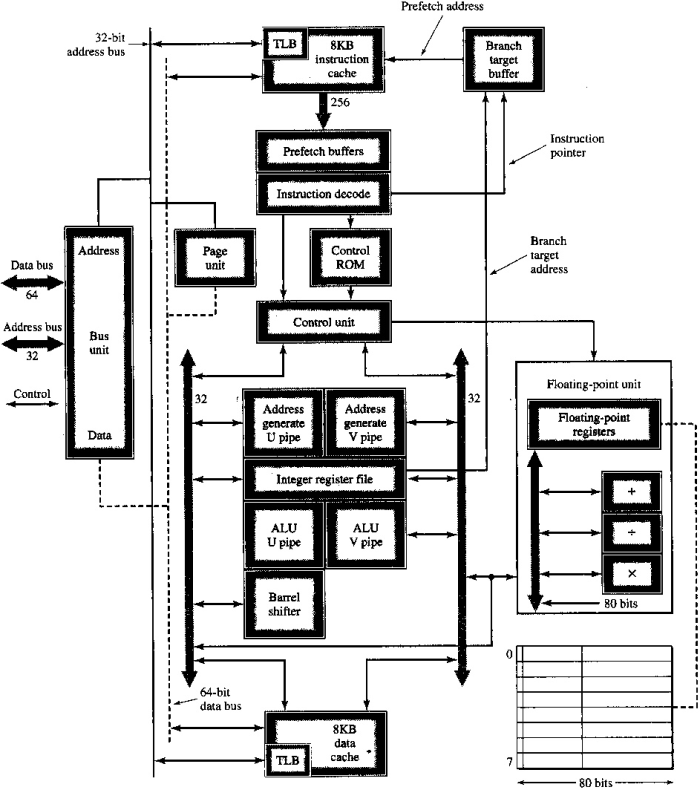

Von Neumann computer systems contain three main building blocks:

-

the central processing unit (CPU),

-

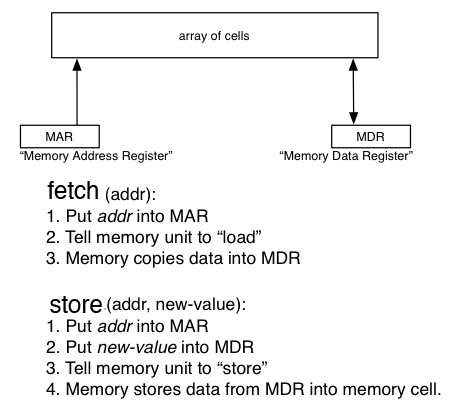

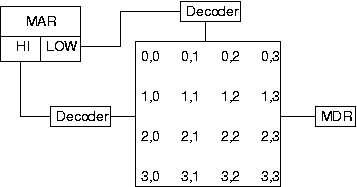

memory,

-

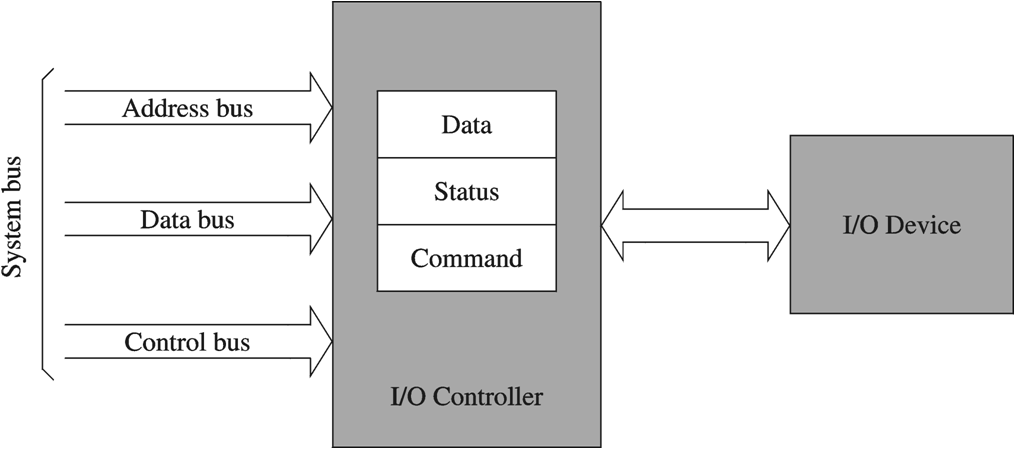

and input/output devices (I/O).

-

-

These three components are connected together using the system bus.

-

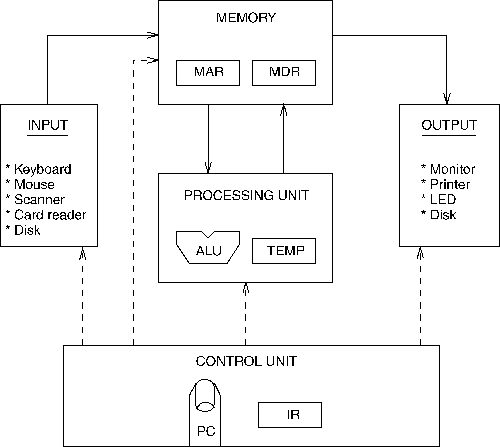

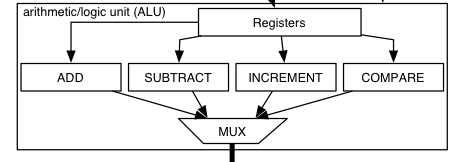

The most prominent items within the CPU are the registers: they can be manipulated directly by a computer program.

-

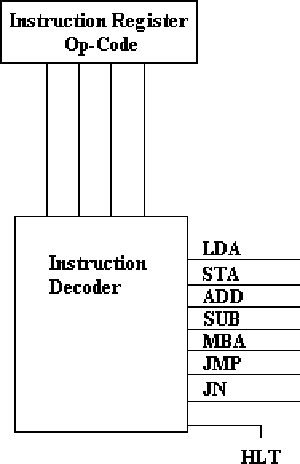

The following block diagram shows major relationship between CPU components: